SuperSimpleController(その12)プリント基板完成 [OriginalCPU]

前回の記事の冒頭に書いたように「SuperSimpleController(その9)回路図とパターン設計」の記事で書いたプリント基板が製造依頼したElecrowさんから届き、部品実装してみたので記録しておきます。

製造依頼は5枚ですが6枚届きました(Elecrowさんのいつものサービスですね)

レジスト色は青にしています。下の写真がトップ面で特に問題ない仕上がりです。今回は10cm四方の基板にかなり詰め込んだので、トラック幅も部分的(SMD IC部品の周辺等)に最小値(0.15mm)に近い0.16mm幅のものを使いましたが問題なく製造されています。

設計上の問題ですが、LEDのマイナス側を示す二重線が、シルク上ほとんど区別は付かない状態だったので次回はシルクを変更する必要があります。

また中央上部にあるHALTのLEDの極性が逆でしたw。このLEDは当初RUN LEDとして付けたものをパターン設計中にHALT時に点灯するように変更したものです。

下の写真はボトム面で左上のSMDタイプの74HC574のICの下側のパスコンが半分程度ICに重なっていましたw。

設計上のミスですがこのICはトップ面でもほぼ同じ位置に74HC574があるのでトップ面のICとの重なりだけをチェックしてしまっていたようです(部品の3Dデータが揃っていないので3D表示でのチェックはしていなかった^^;)。

今回はこのパスコンを未実装にして組み立てています。

手書きのラベルが汚くて恐縮ですが部品実装後のトップ面が下の写真です。

クロック上限が未評価で当面は外部からクロックを供給して動かすつもりなので水晶は未実装のままです。

注文していた丸ピンソケットがまだ届いていないので、EEPROMは平ピンソケットを二重に重ねてゼロプレッシャーソケットを付けました。

ALUのM27C322は42ピンなので32ピンの平ピンソケット+10ピン分削り加工したもので対応しています。

青色LEDはVf:3V想定で電流制限抵抗を2Kにしましたが、眩しすぎるくらい明るいです(最近の青色LEDはVfが低い?)

また、halt表示のLEDは通常動作時はDuty10%程度でhalt時にDuty100%になる設計(ハードリソース最小化のため専用の制御信号を待たない節約設計ですw)ですが、通常動作時でも十分明るいのでhalt表示機能としてはイマイチかもしれません。

ボトム面が下図で追加で縦方向のトラックが引けないくらい混雑しています。上述のように一部のトラック幅を0.16mmにしていますが、見た目はそれ程細くないように見えますね。

下の写真は動作中の状態で、前回の記事で書いたHexLoaderを動かしているところです(シリアルI/Fを付けていないのでロードはできない)。

クロック50Hzで動かすとLE0の点灯状態が目まぐるしく変化して綺麗ですが、クロック1MHzでは変化が殆どありませんw

★追記 2021/03/28

Twitterにポストした動画付きコメントを貼っておきます。

[TOP] [ 前へ ] 連載記事 [ 次へ ]

製造依頼は5枚ですが6枚届きました(Elecrowさんのいつものサービスですね)

レジスト色は青にしています。下の写真がトップ面で特に問題ない仕上がりです。今回は10cm四方の基板にかなり詰め込んだので、トラック幅も部分的(SMD IC部品の周辺等)に最小値(0.15mm)に近い0.16mm幅のものを使いましたが問題なく製造されています。

設計上の問題ですが、LEDのマイナス側を示す二重線が、シルク上ほとんど区別は付かない状態だったので次回はシルクを変更する必要があります。

また中央上部にあるHALTのLEDの極性が逆でしたw。このLEDは当初RUN LEDとして付けたものをパターン設計中にHALT時に点灯するように変更したものです。

| PCBのTOP面 |

|

|

下の写真はボトム面で左上のSMDタイプの74HC574のICの下側のパスコンが半分程度ICに重なっていましたw。

設計上のミスですがこのICはトップ面でもほぼ同じ位置に74HC574があるのでトップ面のICとの重なりだけをチェックしてしまっていたようです(部品の3Dデータが揃っていないので3D表示でのチェックはしていなかった^^;)。

今回はこのパスコンを未実装にして組み立てています。

| PCBのBottom面 |

|

|

手書きのラベルが汚くて恐縮ですが部品実装後のトップ面が下の写真です。

クロック上限が未評価で当面は外部からクロックを供給して動かすつもりなので水晶は未実装のままです。

注文していた丸ピンソケットがまだ届いていないので、EEPROMは平ピンソケットを二重に重ねてゼロプレッシャーソケットを付けました。

ALUのM27C322は42ピンなので32ピンの平ピンソケット+10ピン分削り加工したもので対応しています。

青色LEDはVf:3V想定で電流制限抵抗を2Kにしましたが、眩しすぎるくらい明るいです(最近の青色LEDはVfが低い?)

また、halt表示のLEDは通常動作時はDuty10%程度でhalt時にDuty100%になる設計(ハードリソース最小化のため専用の制御信号を待たない節約設計ですw)ですが、通常動作時でも十分明るいのでhalt表示機能としてはイマイチかもしれません。

| Top面 |

|

|

ボトム面が下図で追加で縦方向のトラックが引けないくらい混雑しています。上述のように一部のトラック幅を0.16mmにしていますが、見た目はそれ程細くないように見えますね。

| Bottom面 |

|

|

下の写真は動作中の状態で、前回の記事で書いたHexLoaderを動かしているところです(シリアルI/Fを付けていないのでロードはできない)。

クロック50Hzで動かすとLE0の点灯状態が目まぐるしく変化して綺麗ですが、クロック1MHzでは変化が殆どありませんw

| 動作中の様子 |

|

|

★追記 2021/03/28

Twitterにポストした動画付きコメントを貼っておきます。

ROMとGALを使ったオリジナルCPUを検討中

— skyriver (@wcinp) March 28, 2021

プリント基板ができ部品も揃ったので部品実装してみた

クロック上限は未評価なので水晶は未実装

動画は外部クロックでステップ動作後50Hzで動かしたものですhttps://t.co/Bdd3aD6eyG#Simple8Z #オリジナルCPU https://t.co/hgqNEjO1oQ pic.twitter.com/N8RcLXjW3K

[TOP] [ 前へ ] 連載記事 [ 次へ ]

SuperSimpleController(その11)HexLoaderの制作 [OriginalCPU]

前回の記事でシリアル通信ができたことを書きましたが、たまに文字化けが発生する状態でした。

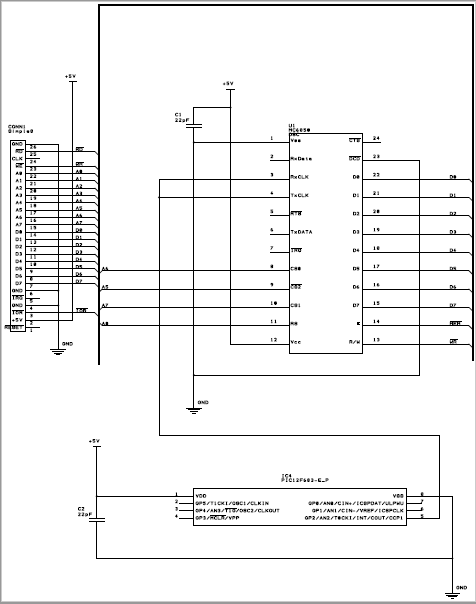

今回開発しているSimple8Z側の問題なのか調査したところ、PICで生成しているSIO(MC6850)用のクロック精度が悪いことが原因だということが判ったのでPIC内蔵クロックから外付けの8MHzクリスタルに変更したところシリアル通信が安定しました。

PICのソースも変更したので貼っておきます。

今回の自作CPU(Simple8Z)には割込み機能は無いので連続した受信データ(9600bsp)の処理は難しいですが、TeraTermの設定でキャラクタ間に時間を設けてやれば処理できるはずです(TeraTermの設定は5ms/char、20ms/lineにしました)。Simple8Zのクロックも1MHzに上げてみました(上限はもっと高いと思う)。

★2021/04/03 追記 {

不安定だった原因はJP関連の命令でクリティカルなタイミングがあったためでuCODEを見直したことで安定になりました。1MHzのクロックで動作時にTeraTermの設定が9600bpsで文字毎のウェイト無し(0ms/char)でも取りこぼしが発生しない状態になりました。また、シリアル通信用クロックもPIC内部発信で154.6KHz(=9600x16)付近のクロックを生成することで文字化けもなくなりました。

}

今後の作業のことも考慮して、まずはヘキサファイルのローダーを作成してみました。前回の記事にマシン語コード表を書きましたが一通りのマシン語を実装したつもりなので、現状のマシン語セットである程度の規模の処理を記述できるかの確認の意味もあります。

ジャンプ命令でR1レジスタが壊れる等、癖がありますが結果としては何とかできました。メモリ上のワーク領域にある2バイトのアドレスデータの示すメモリにレジスタの内容を書込む処理ができなかったので、ワーク領域の直前にWR_RO命令のオペコードを書いてそこをコールするという方法で対応しましたw

作成したHexLoaderのリストは下記になります。処理内容としては「Z80GALの構想(その4)簡易モニタの製作」の記事に書いたHexファイルローダーとほぼ同様で、この時はZ80で約120バイトでしたが、今回は約290バイトなので2倍以上のサイズになってしまいました(但し、今回は自動実行の処理を追加している)。

Simple8Zはレジスタ数が少ない(R0,R1の2個)のでメモリアクセスが多くなることがサイズが大きくなった主な原因だと思います。

HexLoader試験のために作成したテストプログラムはHelloを表示する単純なものです。

上記の試験用プログラムをアセンブル&リンクすることで下記のヘキサファイルが生成されます。

今回作成したHexLoaderはhexFileを1行読む度にレコードタイプを表示するようにしているのでデータ行数分'0'を表示後、終了レコードのレコードタイプである'1'を表示し、ロードしたアプリケーションを実行します。この時の実行アドレスは先頭のデータ行のアドレスにしています。

HexLoaderを起動し、上記の試験用プログラムのHexFileをロードしている様子が下図の画面キャプチャーです。

★追記 2021/03/25

Twitterにポストした動画付きメッセージを貼っておきます。

[TOP] [ 前へ ] 連載記事 [ 次へ ]

今回開発しているSimple8Z側の問題なのか調査したところ、PICで生成しているSIO(MC6850)用のクロック精度が悪いことが原因だということが判ったのでPIC内蔵クロックから外付けの8MHzクリスタルに変更したところシリアル通信が安定しました。

PICのソースも変更したので貼っておきます。

| 8MHzクリスタルでの9.6KHz生成ソース(PIC12F683) |

|

今回の自作CPU(Simple8Z)には割込み機能は無いので連続した受信データ(9600bsp)の処理は難しいですが、TeraTermの設定でキャラクタ間に時間を設けてやれば処理できるはずです(TeraTermの設定は5ms/char、20ms/lineにしました)。Simple8Zのクロックも1MHzに上げてみました(上限はもっと高いと思う)。

★2021/04/03 追記 {

不安定だった原因はJP関連の命令でクリティカルなタイミングがあったためでuCODEを見直したことで安定になりました。1MHzのクロックで動作時にTeraTermの設定が9600bpsで文字毎のウェイト無し(0ms/char)でも取りこぼしが発生しない状態になりました。また、シリアル通信用クロックもPIC内部発信で154.6KHz(=9600x16)付近のクロックを生成することで文字化けもなくなりました。

}

今後の作業のことも考慮して、まずはヘキサファイルのローダーを作成してみました。前回の記事にマシン語コード表を書きましたが一通りのマシン語を実装したつもりなので、現状のマシン語セットである程度の規模の処理を記述できるかの確認の意味もあります。

ジャンプ命令でR1レジスタが壊れる等、癖がありますが結果としては何とかできました。メモリ上のワーク領域にある2バイトのアドレスデータの示すメモリにレジスタの内容を書込む処理ができなかったので、ワーク領域の直前にWR_RO命令のオペコードを書いてそこをコールするという方法で対応しましたw

作成したHexLoaderのリストは下記になります。処理内容としては「Z80GALの構想(その4)簡易モニタの製作」の記事に書いたHexファイルローダーとほぼ同様で、この時はZ80で約120バイトでしたが、今回は約290バイトなので2倍以上のサイズになってしまいました(但し、今回は自動実行の処理を追加している)。

Simple8Zはレジスタ数が少ない(R0,R1の2個)のでメモリアクセスが多くなることがサイズが大きくなった主な原因だと思います。

| 作成したSimple8Z用HexLoaderのソース(アセンブリ言語) |

|

HexLoader試験のために作成したテストプログラムはHelloを表示する単純なものです。

| ローダー試験用プログラム |

|

上記の試験用プログラムをアセンブル&リンクすることで下記のヘキサファイルが生成されます。

| 試験用プログラムのアセンブル&リンクで得られたヘキサファイル |

|

:2080000010255034806034803D50348080804F2FC31380FFB01980C004804098C03A3A2F37 :15802000C5198090C1E048656C6C6F2C776F726C640D0A00005D :00000001FF |

今回作成したHexLoaderはhexFileを1行読む度にレコードタイプを表示するようにしているのでデータ行数分'0'を表示後、終了レコードのレコードタイプである'1'を表示し、ロードしたアプリケーションを実行します。この時の実行アドレスは先頭のデータ行のアドレスにしています。

HexLoaderを起動し、上記の試験用プログラムのHexFileをロードしている様子が下図の画面キャプチャーです。

| HexLoader実行画面例 |

|

|

★追記 2021/03/25

Twitterにポストした動画付きメッセージを貼っておきます。

ROMとGALを使ったオリジナルCPUを検討中

— skyriver (@wcinp) March 25, 2021

MC6850を接続してシリアル通信ができるようになったのでヘキサファイルのローダーを作成しました

これでアセンブルしたAPのロード作業が楽になり、いよいよCPUらしくなってきた^^https://t.co/lb2uduYhmj#Simple8Z #オリジナルCPU pic.twitter.com/6A4AjXq71B

[TOP] [ 前へ ] 連載記事 [ 次へ ]

SuperSimpleController(その10)I/O命令追加 [OriginalCPU]

前回の記事で書いたプリント基板はElecrowさんから昨日(2021/03/20)届いたのですが、手配中の74HCU04のSMDタイプがまだ届いていないので部品待ち状態です。

今回はI/O関連のマシン語の実装について書いてみます。

下表がマシン語コード表のアップデート版で橙色の部分が今回追加したマシン語です。マシン語実行時に影響を受けるレジスタを記入した「register」カラムを追記しました。

従来、CALL命令とRET命令ではR0とR1レジスタが破壊されていましたが、プログラムの実行効率が悪くなるのでR0は保存されるように改善しています(このためRET命令のクロックが20から22に増加した)

I/O命令でのアドレスは直値の方法とR1レジスタ指定の二通りを実装しました。

また、I/O命令の他にRX(=R1:R0レジスタペア)とPCとの相互のロード命令とRXへの直値ロード命令も追加しました。

今回実施したマシン語の試験用ソースのリストが下記になります。

I/O命令を追加したのでHelloを表示後に入力をエコーバックするというシリアル通信処理を想定した内容にしています。

折角なので手持ちにあったシリアル通信用チップ(MC68B50)をブレッドボード上で仮接続して試験しました。通信用クロックはPIC12F683を使って9.6KHzを生成し、MC68B50に供給しています。

MC68B50のE信号(チップイネーブル)は正論理なので本来ならSimple8Zの外部接続用コネクタ内のIOR/信号(MEM/信号を反転したもの)を反転して接続すべきですが、動作試験ということでMEM/信号を直接接続しました。

試験用ソフト内のPUTC処理のRET命令実行直後に停止させた際のロジアナ画面が下図になります。

12:IRW/が命令フェッチ信号でこの信号が0の箇所がマシン語の区切りです。

シリアル通信で"Hello"の最初の'H'を出力している部分を拡大したものが下図です。

確かに'H'が出力されています^^

★追記 2021/03/22 {

上図ではディバッグのためにクロックを50Hzにしているので'H'のシリアル出力時間と比較しCPUの動作がかなり遅くなっています。クロックを約130KHzにした場合のロジアナ波形が下図になります。クロック上限は未評価です。

}

上記の試験用ソースにあるエコーバック部分に関してはまだ動作確認できていませんが、MC68B50のTxDataとRxDataにシリアルUSB変換モジュールを接続してTeraTermでモニタした結果が下図になります。

CPUボードを組み立てた際に多くの人が出力するであろうなんの変哲もないただのハロー表示画面ですが、今回は自作のCPUで出したものなので感慨深いものがありますね。

★追記 2021/03/22

エコーバック試験も通りました^^

ノートPCのTeraTermのバックカラーは暗かったということが判ったw

[TOP] [ 前へ ] 連載記事 [ 次へ ]

今回はI/O関連のマシン語の実装について書いてみます。

下表がマシン語コード表のアップデート版で橙色の部分が今回追加したマシン語です。マシン語実行時に影響を受けるレジスタを記入した「register」カラムを追記しました。

従来、CALL命令とRET命令ではR0とR1レジスタが破壊されていましたが、プログラムの実行効率が悪くなるのでR0は保存されるように改善しています(このためRET命令のクロックが20から22に増加した)

I/O命令でのアドレスは直値の方法とR1レジスタ指定の二通りを実装しました。

また、I/O命令の他にRX(=R1:R0レジスタペア)とPCとの相互のロード命令とRXへの直値ロード命令も追加しました。

今回実施したマシン語の試験用ソースのリストが下記になります。

I/O命令を追加したのでHelloを表示後に入力をエコーバックするというシリアル通信処理を想定した内容にしています。

| 今回実施した試験プログラム(アセンブリ言語) |

|

折角なので手持ちにあったシリアル通信用チップ(MC68B50)をブレッドボード上で仮接続して試験しました。通信用クロックはPIC12F683を使って9.6KHzを生成し、MC68B50に供給しています。

| シリアル通信用クロックgenelator(PIC12F683) |

|

MC68B50のE信号(チップイネーブル)は正論理なので本来ならSimple8Zの外部接続用コネクタ内のIOR/信号(MEM/信号を反転したもの)を反転して接続すべきですが、動作試験ということでMEM/信号を直接接続しました。

| 追加したシリアルチップ(MC68B50) |

|

試験用ソフト内のPUTC処理のRET命令実行直後に停止させた際のロジアナ画面が下図になります。

12:IRW/が命令フェッチ信号でこの信号が0の箇所がマシン語の区切りです。

| 試験用ソフト実行時のロジアナ画面例 |

|

|

シリアル通信で"Hello"の最初の'H'を出力している部分を拡大したものが下図です。

確かに'H'が出力されています^^

| 試験用ソフト実行時のロジアナ画面例('H'出力部) |

|

|

★追記 2021/03/22 {

上図ではディバッグのためにクロックを50Hzにしているので'H'のシリアル出力時間と比較しCPUの動作がかなり遅くなっています。クロックを約130KHzにした場合のロジアナ波形が下図になります。クロック上限は未評価です。

| クロック約130KHzでの'H'出力 |

|

|

上記の試験用ソースにあるエコーバック部分に関してはまだ動作確認できていませんが、MC68B50のTxDataとRxDataにシリアルUSB変換モジュールを接続してTeraTermでモニタした結果が下図になります。

CPUボードを組み立てた際に多くの人が出力するであろうなんの変哲もないただのハロー表示画面ですが、今回は自作のCPUで出したものなので感慨深いものがありますね。

| Simple8Zでの初めてのHello,world |

|

|

★追記 2021/03/22

エコーバック試験も通りました^^

ノートPCのTeraTermのバックカラーは暗かったということが判ったw

| エコーバックもOK |

|

|

[TOP] [ 前へ ] 連載記事 [ 次へ ]

SuperSimpleController(その9)回路図とパターン設計 [OriginalCPU]

前回の記事で書いたようにマシン語の実装も概ねできて(今後I/O関連等のマシン語を追加予定)ハード的にも安定しているようなので回路図の整理とパターン設計を行いました。

結果として13チップ構成となり 10cm x 10cm のプリント基板にかろうじて実装することができました^^

外部とのインターフェースは実装できなかったのでI/Oインターフェースとしてアドレス、データ及び最小限の制御信号をコネクタ接続できるようにしています。

この外部インターフェースのコネクタの信号配列は Simple8 というバス仕様に準拠しました(オリジナルCPUの名前を決めるためのグーグラビリティの確認時に見つけたw)

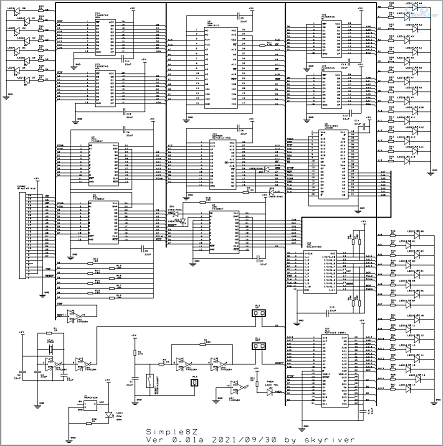

今までの評価で多少の変更があったのでブロック図も更新しました。この図から構成チップと回路図の大枠が判るのではないかと思います。

今回のオリジナルCPUは上述のように13チップ構成で、4itCPUでメジャーなTD4が14チップ構成なので64KBのメモリ空間を有する8bitCPUとしてはかなりシンプルな回路にできたのではないでしょうか?

★追記 2021/03/15

上記のTD4のチップ数はネット上にあった制作例の写真からカウントしましたが「CPUの創りかた」の書籍の表紙には”IC10個のお手軽CPU”との記載がありました

「開発環境について」の記事で書いたように動作確認時に外部からクロックとリセット信号を供給することで任意時点で動作停止できていたのでこの環境も継続して使えるようにジャンパーピンを追加しました。クロックは1MHz付近までは動くことを確認しましたが、上限は未確認です。またLEDの電流制限抵抗値等も今後見直す可能性があります(手配中のLEDがきたら実験予定)

詳細は下記の回路図を参照してください。

パターン設計はかなり難航(特に縦方向の経路が殆どなくなった)しましたが、詰む寸前で最後のトラックを何とか通すことができました^^

HC574周りは最小トラック幅(0.16mm:Elecrowでは0.15mmですがFusion PCBでは6milで切り上げ計算すると0.16mm)で配線しましたがviaの最小幅が0.6mm(ホール0.3mmで枠が0.15mmx2)なのでトラック間の隙間もある程度必要になり、top面とbottom面で縦横直行パターンにするより斜めにしてviaを少なくした方が効率がいい場合もあることが判りました。

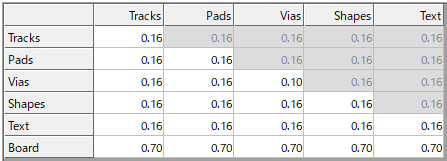

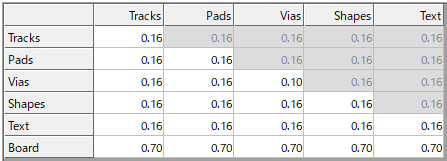

DesignSparkPCBでのSpaceingsのチェック設定は下表の値で通しています。

尚、DCプラグのGND端子の中央部分で下記のエラーが最後まで取れませんでしたが、拡大表示して該当するようなパターンもなく、悪さしそうもないのでそのままにしていますw

Dangling Track from (538.40,542.08) to (538.54,542.29) on layer Top Copper

完成したプリント基板のパターンが下図になります。

緑色の部分はグランドです。未結線であることを示す細い線が残っていますが、グランドをベタパターンにする時点で接続されます(孤立した場合はviaを打ってつなげる)

グランドベタ化後のトップ面とボトム面が下図になります。

去年の暮れ頃にElecrowさんにPic24V20の基板を手配した際に貰った555ポイントがまだ有効だったのでElecrowさんに本日製造依頼しました。

100ポイントで1ドル相当でポイント適用を555で入力したら1回に使えるポイント数は購入価格の40%までのようでポイントで-$1.96値引きされ、未使用分は残ポイントとして残りました。

また、今回は5枚製造依頼し、基板の厚さをちょっと薄めの1.2mmにしてみました(軽い方が輸送費が安くなるw)。

輸送方法は安めのOCS/ANA Express(3-5 Business Days)にしています(因みにDHLでは$18.72)

最後にElecrowさんに依頼する際に必要になる設計データファイルのリネームについてDesignSparkPCBの出力ファイル名との対応をメモしておきます。

★追記 2021/04/17

構成チップ一覧表を追記します。

[TOP] [ 前へ ] 連載記事 [ 次へ ]

結果として13チップ構成となり 10cm x 10cm のプリント基板にかろうじて実装することができました^^

外部とのインターフェースは実装できなかったのでI/Oインターフェースとしてアドレス、データ及び最小限の制御信号をコネクタ接続できるようにしています。

この外部インターフェースのコネクタの信号配列は Simple8 というバス仕様に準拠しました(オリジナルCPUの名前を決めるためのグーグラビリティの確認時に見つけたw)

今までの評価で多少の変更があったのでブロック図も更新しました。この図から構成チップと回路図の大枠が判るのではないかと思います。

| Simple8Z概要ブロック図 |

|

★変更 2021/11/03 ブロック図を最新版にアップデート |

今回のオリジナルCPUは上述のように13チップ構成で、4itCPUでメジャーなTD4が14チップ構成なので64KBのメモリ空間を有する8bitCPUとしてはかなりシンプルな回路にできたのではないでしょうか?

★追記 2021/03/15

上記のTD4のチップ数はネット上にあった制作例の写真からカウントしましたが「CPUの創りかた」の書籍の表紙には”IC10個のお手軽CPU”との記載がありました

「開発環境について」の記事で書いたように動作確認時に外部からクロックとリセット信号を供給することで任意時点で動作停止できていたのでこの環境も継続して使えるようにジャンパーピンを追加しました。クロックは1MHz付近までは動くことを確認しましたが、上限は未確認です。またLEDの電流制限抵抗値等も今後見直す可能性があります(手配中のLEDがきたら実験予定)

詳細は下記の回路図を参照してください。

| Simple8Zの回路図 |

|

| ★変更 2021/11/03 最新版にアップデート |

パターン設計はかなり難航(特に縦方向の経路が殆どなくなった)しましたが、詰む寸前で最後のトラックを何とか通すことができました^^

HC574周りは最小トラック幅(0.16mm:Elecrowでは0.15mmですがFusion PCBでは6milで切り上げ計算すると0.16mm)で配線しましたがviaの最小幅が0.6mm(ホール0.3mmで枠が0.15mmx2)なのでトラック間の隙間もある程度必要になり、top面とbottom面で縦横直行パターンにするより斜めにしてviaを少なくした方が効率がいい場合もあることが判りました。

DesignSparkPCBでのSpaceingsのチェック設定は下表の値で通しています。

尚、DCプラグのGND端子の中央部分で下記のエラーが最後まで取れませんでしたが、拡大表示して該当するようなパターンもなく、悪さしそうもないのでそのままにしていますw

完成したプリント基板のパターンが下図になります。

緑色の部分はグランドです。未結線であることを示す細い線が残っていますが、グランドをベタパターンにする時点で接続されます(孤立した場合はviaを打ってつなげる)

| 完成したプリント基板のパターン(グランドベタ化前) |

|

|

グランドベタ化後のトップ面とボトム面が下図になります。

| トップ面(グランドベタ化後) |

|

|

| ボトム面(グランドベタ化後) |

|

|

去年の暮れ頃にElecrowさんにPic24V20の基板を手配した際に貰った555ポイントがまだ有効だったのでElecrowさんに本日製造依頼しました。

100ポイントで1ドル相当でポイント適用を555で入力したら1回に使えるポイント数は購入価格の40%までのようでポイントで-$1.96値引きされ、未使用分は残ポイントとして残りました。

| Subtotal | $4.90 |

| Rewardpoints(Used 196) | -$1.96 |

| Shipping & Handling | $13.90 |

| Estimated Total | $16.84 |

また、今回は5枚製造依頼し、基板の厚さをちょっと薄めの1.2mmにしてみました(軽い方が輸送費が安くなるw)。

輸送方法は安めのOCS/ANA Express(3-5 Business Days)にしています(因みにDHLでは$18.72)

最後にElecrowさんに依頼する際に必要になる設計データファイルのリネームについてDesignSparkPCBの出力ファイル名との対応をメモしておきます。

| No. | DSPCB output | new file name |

|---|---|---|

| 1 | Simple8Z001 - Top Copper.gbr | Simple8Z001.GTL |

| 2 | Simple8Z001 - Top Silkscreen.gbr | Simple8Z001.GTO |

| 3 | Simple8Z001 - Top Copper (Resist).gbr | Simple8Z001.GTS |

| 4 | Simple8Z001 - Bottom Copper.gbr | Simple8Z001.GBL |

| 5 | Simple8Z001 - Bottom Silkscreen.gbr | Simple8Z001.GBO |

| 6 | Simple8Z001 - Bottom Copper (Resist).gbr | Simple8Z001.GBS |

| 7 | Simple8Z001 - Drill Data - [Through Hole].drl | Simple8Z001.TXT |

| 8 | Simple8Z001 - Outline.gbr | Simple8Z001.GML |

★追記 2021/04/17

構成チップ一覧表を追記します。

| 構成チップ一覧 |

|

|

[TOP] [ 前へ ] 連載記事 [ 次へ ]