SuperSimpleController(その10)I/O命令追加 [OriginalCPU]

前回の記事で書いたプリント基板はElecrowさんから昨日(2021/03/20)届いたのですが、手配中の74HCU04のSMDタイプがまだ届いていないので部品待ち状態です。

今回はI/O関連のマシン語の実装について書いてみます。

下表がマシン語コード表のアップデート版で橙色の部分が今回追加したマシン語です。マシン語実行時に影響を受けるレジスタを記入した「register」カラムを追記しました。

従来、CALL命令とRET命令ではR0とR1レジスタが破壊されていましたが、プログラムの実行効率が悪くなるのでR0は保存されるように改善しています(このためRET命令のクロックが20から22に増加した)

I/O命令でのアドレスは直値の方法とR1レジスタ指定の二通りを実装しました。

また、I/O命令の他にRX(=R1:R0レジスタペア)とPCとの相互のロード命令とRXへの直値ロード命令も追加しました。

今回実施したマシン語の試験用ソースのリストが下記になります。

I/O命令を追加したのでHelloを表示後に入力をエコーバックするというシリアル通信処理を想定した内容にしています。

折角なので手持ちにあったシリアル通信用チップ(MC68B50)をブレッドボード上で仮接続して試験しました。通信用クロックはPIC12F683を使って9.6KHzを生成し、MC68B50に供給しています。

MC68B50のE信号(チップイネーブル)は正論理なので本来ならSimple8Zの外部接続用コネクタ内のIOR/信号(MEM/信号を反転したもの)を反転して接続すべきですが、動作試験ということでMEM/信号を直接接続しました。

試験用ソフト内のPUTC処理のRET命令実行直後に停止させた際のロジアナ画面が下図になります。

12:IRW/が命令フェッチ信号でこの信号が0の箇所がマシン語の区切りです。

シリアル通信で"Hello"の最初の'H'を出力している部分を拡大したものが下図です。

確かに'H'が出力されています^^

★追記 2021/03/22 {

上図ではディバッグのためにクロックを50Hzにしているので'H'のシリアル出力時間と比較しCPUの動作がかなり遅くなっています。クロックを約130KHzにした場合のロジアナ波形が下図になります。クロック上限は未評価です。

}

上記の試験用ソースにあるエコーバック部分に関してはまだ動作確認できていませんが、MC68B50のTxDataとRxDataにシリアルUSB変換モジュールを接続してTeraTermでモニタした結果が下図になります。

CPUボードを組み立てた際に多くの人が出力するであろうなんの変哲もないただのハロー表示画面ですが、今回は自作のCPUで出したものなので感慨深いものがありますね。

★追記 2021/03/22

エコーバック試験も通りました^^

ノートPCのTeraTermのバックカラーは暗かったということが判ったw

[TOP] [ 前へ ] 連載記事 [ 次へ ]

今回はI/O関連のマシン語の実装について書いてみます。

下表がマシン語コード表のアップデート版で橙色の部分が今回追加したマシン語です。マシン語実行時に影響を受けるレジスタを記入した「register」カラムを追記しました。

従来、CALL命令とRET命令ではR0とR1レジスタが破壊されていましたが、プログラムの実行効率が悪くなるのでR0は保存されるように改善しています(このためRET命令のクロックが20から22に増加した)

I/O命令でのアドレスは直値の方法とR1レジスタ指定の二通りを実装しました。

また、I/O命令の他にRX(=R1:R0レジスタペア)とPCとの相互のロード命令とRXへの直値ロード命令も追加しました。

今回実施したマシン語の試験用ソースのリストが下記になります。

I/O命令を追加したのでHelloを表示後に入力をエコーバックするというシリアル通信処理を想定した内容にしています。

| 今回実施した試験プログラム(アセンブリ言語) |

|

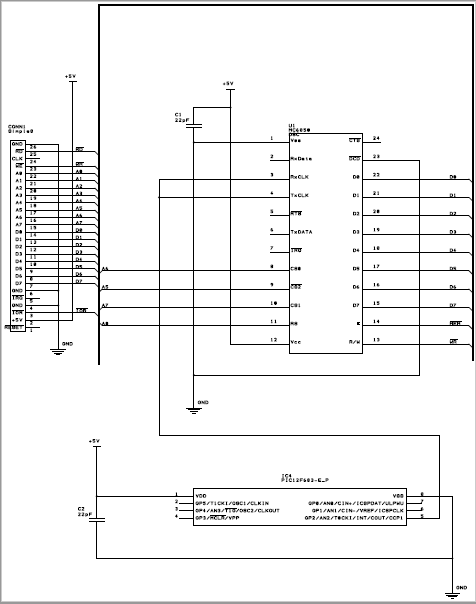

折角なので手持ちにあったシリアル通信用チップ(MC68B50)をブレッドボード上で仮接続して試験しました。通信用クロックはPIC12F683を使って9.6KHzを生成し、MC68B50に供給しています。

| シリアル通信用クロックgenelator(PIC12F683) |

|

MC68B50のE信号(チップイネーブル)は正論理なので本来ならSimple8Zの外部接続用コネクタ内のIOR/信号(MEM/信号を反転したもの)を反転して接続すべきですが、動作試験ということでMEM/信号を直接接続しました。

| 追加したシリアルチップ(MC68B50) |

|

試験用ソフト内のPUTC処理のRET命令実行直後に停止させた際のロジアナ画面が下図になります。

12:IRW/が命令フェッチ信号でこの信号が0の箇所がマシン語の区切りです。

| 試験用ソフト実行時のロジアナ画面例 |

|

|

シリアル通信で"Hello"の最初の'H'を出力している部分を拡大したものが下図です。

確かに'H'が出力されています^^

| 試験用ソフト実行時のロジアナ画面例('H'出力部) |

|

|

★追記 2021/03/22 {

上図ではディバッグのためにクロックを50Hzにしているので'H'のシリアル出力時間と比較しCPUの動作がかなり遅くなっています。クロックを約130KHzにした場合のロジアナ波形が下図になります。クロック上限は未評価です。

| クロック約130KHzでの'H'出力 |

|

|

上記の試験用ソースにあるエコーバック部分に関してはまだ動作確認できていませんが、MC68B50のTxDataとRxDataにシリアルUSB変換モジュールを接続してTeraTermでモニタした結果が下図になります。

CPUボードを組み立てた際に多くの人が出力するであろうなんの変哲もないただのハロー表示画面ですが、今回は自作のCPUで出したものなので感慨深いものがありますね。

| Simple8Zでの初めてのHello,world |

|

|

★追記 2021/03/22

エコーバック試験も通りました^^

ノートPCのTeraTermのバックカラーは暗かったということが判ったw

| エコーバックもOK |

|

|

[TOP] [ 前へ ] 連載記事 [ 次へ ]

2021-03-21 12:37

nice!(0)

コメント(0)

コメント 0