SuperSimpleController(その20)TMS9918Aの接続 その5 [OriginalCPU]

東京2020オリンピックも終わったので「SuperSimpleController(その19)TMS9918Aの接続 その4」の記事で書き掛けの自作CPU基板(Simple8Z)用に作った下の写真のビデオボード(Simpe8VDPSG)のハードディバッグ状況について記録しておきます。

結果としては無事に安定して画面表示ができるようになりました^^

TMS9918への4bitDRAMの接続例はネット上には見当たらなかったので珍しい試みだと思います(4bitDRAMを接続するならTMS9118等を使用するのが通例)

前回の記事でDRAMへのリード/ライト信号の調整を行ったので今回はDRAMへのRAS/CAS信号のタイミングやVDP(TMS9918)へのライトタイミングの調整を行いました。

[TOP] [ 前へ ] 連載記事 [ 次へ ]

結果としては無事に安定して画面表示ができるようになりました^^

TMS9918への4bitDRAMの接続例はネット上には見当たらなかったので珍しい試みだと思います(4bitDRAMを接続するならTMS9118等を使用するのが通例)

| VDPSG on Simple8Z |

|

|

前回の記事でDRAMへのリード/ライト信号の調整を行ったので今回はDRAMへのRAS/CAS信号のタイミングやVDP(TMS9918)へのライトタイミングの調整を行いました。

- DRAMへのRAS/CASタイミング

DRAMへのライト時のRAS/CAS信号のタイミングは下図のような感じで特に問題無いように見えます。

DRAM Write timing(OK pattern) サンプリング:50MHz

DRAMからのリード時のRAS/CAS信号例が下図でこちらも特に問題ないように見えます。

DRAM Read timing(OK pattern) サンプリング:50MHz

しかし、下図のようにCAS/の立下りとアドレス(A0)の変化が同じタイミングのNGパターンが散見されました。

アドレス信号が変化後、CAS/が立ち下がることでDRAMがカラムアドレスをラッチするのが本来のシーケンスのはずです。尚、ロジアナのサンプリング周期は50MHzなので時間分解能は20nsになります。

DRAM RAS/CAS timing(NG pattern) サンプリング:50MHz

対策としてDRAMに供給するCAS/信号を遅らせるために未使用のORゲートを追加しました。全体の回路図は「SuperSimpleController(その17)」の記事を参照してください。

CAS/信号生成部にORゲート追加

対策後の波形を確認したところ、上記のNGパターンのようにCAS/とアドレス信号が同時に変化するようなパターンは無くなりました。

波形サンプルが下図になります。図中のVDP_CAS/はVDP(TMS9918)から出力されるCAS/信号でアドレスと同時に変化しています(この時のロジアナの時間分解能は25nsなので実際にはCAS/の方が後で変化しているものと推測されます)

対策後のDRAM RAS/CAS timing サンプリング:40MHz

上記の改造を施した基板の写真も貼っておきます。未使用ゲートの入力は両面でベタグランドにサーマルパッドで4点接続されていてグランドからの切り離しが困難なのでシングルラインの丸ピンソケットの1ピン分を使ってICのピンを曲げて接続しました。

プリント基板の改造

下の写真が改造後のボトム面になります。

プリント基板の改造(ボトム面)

対処後の動作としては前回の記事に掲載した画面表示例よりも若干ゴミ表示が少なくなりましたが、まだ、問題がありそうです。 - VDP(TMS9918)のライトサイクル

VDPとDRAM間の制御信号の確認はできたのでCPUとVDP間のI/F信号の確認を行います。

VDPに対するライトサイクルのタイミングチャートを下図に示します。

VDPのライトサイクル

今回のオリジナルCPUのI/O命令ではリードやライト信号がディセーブルになると同時にデータバス上のデータも切り替わるので上図のth(WH-D)の仕様を満たしていません。

更にVDPへのライト信号はアドレスディコード後のセレクト信号とANDしているのでデータバス上のデータよりもゲートでの遅延分、遅れてしまいます。

ロジアナで確認したライト時の波形が下図になります。

尚、自作CPUは暫定的に約1MHzのクロックで動かしています。

VDPライト時のロジアナ波形例(修正前) サンプリング:100MHz

上述のようにライト信号立上りと同時にデータバス上のデータも変化しているのでVDPの規格を満たしていません。

今回のオリジナルCPUのI/Oライト命令はI/Oアドレスを指定するのにイミーデット値の場合とR1レジスタ値の二通りの命令を実装しています(出力値はR0レジスタで指定)

前者のマイクロコードは8ワードで次のマイクロコードが直後に書かれているのでマイクロコードを追加するのが難しいですが、後者のマイクロコードは7ワードなので1ワード追加してライト信号立上り後も1クロック分データを保持するようにしました。

マイクロコードの具体的な変更部分は下記の黄色部分になります。

I/Oライトのマイクロコード修正内容 CSTART 0A0H ; ** OUT (R1),R0 CLR IRW CLR RD ACT ALUR CLR PWEN ACT ADW PCLOAD CODE ; 1:AD <- PC, data-bus:R1, set load-mode CLR ADW ACT PWEN ACT PLW CLR MEM ACT WR CODE ; 2:PCL <- R1, data-bus:R0 CLR PLW CLR WR ACT MEM ;; CLR ALUR ;; ACT ALR CODE ; 3: CLR ALUR ACT ALR CODE ; 3: CLR ALR ACT PLW CODE ; 4:PCL <- ADL CLR PLW PCINC CODE ; 5:set inc-mode ACT PLW ACT RD CODE ; 6:inc PC ENDCODE ; 7:

マイクロコード修正後のI/Oライト時のロジアナ波形が下図になります。ライト信号が立上り後、1クロック分ライトデータを保持しています。

VDPライト時のロジアナ波形例(修正後) サンプリング:100MHz

以上の対処でVDPとDRAM間及びCPUとVDP間の信号が確認でき、下の写真のように安定して画面表示できるようになりました^^

VDP(TMS9918)による表示例

★追記 2021/08/21 {

バックカラーをシアン(R07=07H)、テキストのバックカラーをダークブルー(テキストカラーの値をF4H)にしたMSX風の画面を貼っておきます。

VDP(TMS9918)による表示例2

- VDP(TMS9918)のドライブ電流

補足としてVDPのドライブ能力について書いておきます。

VDPの出力ピンの吐出しと吸い込み電流は最大100uAしかなく、ドライブ能力はかなり非力です。

VDP(TMS9918)の規格

VDPはHCTシリーズでインターフェースを取っているので問題ないだろうと思いますが、下図のようにTTL規格表に記載されている74245の規格ではHCTの入力電流が未記載になっています(最大100uAで駆動すれば問題ないように思います)

74245の規格

しかし、「74HC と 74HCT の内部回路の違い」のサイトの内容を参照させて頂くと「HCT シリーズに TTL の H レベル信号を入力すると、mA オーダの消費電流が流れてしまいます」ということなので、何かしらの原因で信号のエッジが鈍った場合等には問題が発生するかもしれません。

因みにDRAM(uPD41464)側の規格は下図で負荷的にはかなり軽くなっているのでVDPに直接接続する場合は問題ありません。

DRAM(uPD41464)の規格

[TOP] [ 前へ ] 連載記事 [ 次へ ]

SuperSimpleController(その19)TMS9918Aの接続 その4 [OriginalCPU]

本ブログで画像データが表示されない問題の対策のためにhttps対応のレンタルサーバを借りたり、ブログ内の画像ファイルのリンクを変更する等の作業が終わったのでオリジナルCPUへのビデオプロセッサ(TMS9918)接続について、前回の記事からだいぶ時間が空いてしまいましたが、動作確認状況について少し書いてみます(まだ動いていません^^;)

VDP(TMS9918)とPSG(AY-3-8910)とシリアル(MC68B50)を搭載し、プリント基板化したSimple8VDPSGをオリジナルCPUに載せた状態が下の写真になります(再掲)。

CPU基板では74AS867が結構熱くなるし、VDPSG基板ではTMS9918が結構熱くなります。2枚の基板を接続した際の消費電流は下の写真のように 0.81A 程度になります。

消費電流が大きいため基板上の電源電圧は 4.74V 程度までに低下してしまいます。

因みに基板間はピンヘッダで接続(+5Vはピン1本、GNDはピン2本)ですが基板間の電源電圧差はほとんどありませんでした。

USBコネクタとプリント基板上の電源部分との抵抗値を実測した結果は5V及びグランド共に0.2~0.3Ωでした。

5V動作で1A程度以上の電流が必要なプリント基板についてはUSB給電以外の電源を考えた方がいいかもしれません(当然、基板上の回路の最低電圧値にも依存)

主要部品の電源電圧規格を下表に示します。

下の写真はUSB給電している様子です。

シリアル通信はすぐに動きましたが、VDPの表示がうまく出ませんorz

DRAMのリード&ライトがうまくできていないようです(上位4bitは'1'固定で下位4bitは初期値?)

DRAMの信号をロジアナで確認した結果が下図で、ライトサイクルで WE/ がアクティブになる直前に一瞬 OE/ がアクティブになってしまっています。

※追記 2021/07/11 {

OE/ のタイミング調整用のコンデンサは前々回の記事に書いた回路図のC11の部分です。回路図では150pFとなっていますが100pFを実装してしまっていましたorz

}

OE/ 信号のタイミング調整用のコンデンサを120pF、150pFにした場合のロジアナ波形が下図です。

両者共に上記の問題は解消していますがリードアクセス時間のマージンが大きい 120pF を採用することにしました。

本来ならこのようなアナログ的な調整は極力避けたいのですが、今回は同期回路にするための都合の良い信号が無かった^^;

念のためにDRAMをブレッドボードで評価した際に使用していたものに交換し、画面表示したサンプルが下の写真です。

4,5行目の"Hello・・"はテストプログラムで書いたもので、1行目の"@ABC・・"と9行目の'123・・"は自作モニタのI/O命令を使って手動で書いたものです。

バックグランドにゴミが多く発生していて画面クリアがうまく行っていない模様です(それにしてはフォントデータの書込みはうまく行っているように見える・・でも'J'等にゴミが載ってますね)

[TOP] [ 前へ ] 連載記事 [ 次へ ]

VDP(TMS9918)とPSG(AY-3-8910)とシリアル(MC68B50)を搭載し、プリント基板化したSimple8VDPSGをオリジナルCPUに載せた状態が下の写真になります(再掲)。

| VDPSG on Simple8Z |

|

|

CPU基板では74AS867が結構熱くなるし、VDPSG基板ではTMS9918が結構熱くなります。2枚の基板を接続した際の消費電流は下の写真のように 0.81A 程度になります。

消費電流が大きいため基板上の電源電圧は 4.74V 程度までに低下してしまいます。

因みに基板間はピンヘッダで接続(+5Vはピン1本、GNDはピン2本)ですが基板間の電源電圧差はほとんどありませんでした。

USBコネクタとプリント基板上の電源部分との抵抗値を実測した結果は5V及びグランド共に0.2~0.3Ωでした。

5V動作で1A程度以上の電流が必要なプリント基板についてはUSB給電以外の電源を考えた方がいいかもしれません(当然、基板上の回路の最低電圧値にも依存)

主要部品の電源電圧規格を下表に示します。

| device | min[V] | max[V] |

|---|---|---|

| TMS9918 | 4.75 | 5.25 |

| 74HCT | 4.5 | 5.5 |

| 74HC | 2 | 6 |

下の写真はUSB給電している様子です。

| Simple8VDPSG on Simple8Zの消費電流 |

|

|

シリアル通信はすぐに動きましたが、VDPの表示がうまく出ませんorz

DRAMのリード&ライトがうまくできていないようです(上位4bitは'1'固定で下位4bitは初期値?)

| 画面表示の状況 |

|

|

DRAMの信号をロジアナで確認した結果が下図で、ライトサイクルで WE/ がアクティブになる直前に一瞬 OE/ がアクティブになってしまっています。

| DRAMタイミング(C:100pF) sampling:25M |

|

|

※追記 2021/07/11 {

OE/ のタイミング調整用のコンデンサは前々回の記事に書いた回路図のC11の部分です。回路図では150pFとなっていますが100pFを実装してしまっていましたorz

}

OE/ 信号のタイミング調整用のコンデンサを120pF、150pFにした場合のロジアナ波形が下図です。

| DRAMタイミング(C:120pF) sampling:40M |

|

|

| DRAMタイミング(C:150pF) sampling:25M |

|

|

両者共に上記の問題は解消していますがリードアクセス時間のマージンが大きい 120pF を採用することにしました。

本来ならこのようなアナログ的な調整は極力避けたいのですが、今回は同期回路にするための都合の良い信号が無かった^^;

念のためにDRAMをブレッドボードで評価した際に使用していたものに交換し、画面表示したサンプルが下の写真です。

| DRAMタイミング調整後の画面表示サンプル |

|

|

4,5行目の"Hello・・"はテストプログラムで書いたもので、1行目の"@ABC・・"と9行目の'123・・"は自作モニタのI/O命令を使って手動で書いたものです。

バックグランドにゴミが多く発生していて画面クリアがうまく行っていない模様です(それにしてはフォントデータの書込みはうまく行っているように見える・・でも'J'等にゴミが載ってますね)

[TOP] [ 前へ ] 連載記事 [ 次へ ]

SuperSimpleController(その18)TMS9918Aの接続 その3 [OriginalCPU]

前回の記事で書いたプリント基板は2021/05/29にELECROWに注文し、6/8に届きました。

今回は5枚発注したのですがなんと11枚届きました(ELECROWさんではいつも1枚くらい余分に届くのですが今回なんと+6枚w)。

5枚手配したのがどこかで10枚手配の扱いになったようです。また、配達が完了してから発送通知(しかも添付の写真無し)が届きました。

コロナ禍の為か受注処理が少々混乱しているようです。

今回は発送方法を佐川さん(以前は選択肢になかった)に指定したことと残っていたポイントを使ったので結構安く上がりました。

出来上がったプリント基板のトップ面が下の写真です。外観的には特に問題なく綺麗に仕上がっています。

ボトム面も綺麗にできています。

今回使用したRCAジャック(NTSC出力用と音声出力用)は共立エレショップさんから購入したホシデン製のものでフットプリントを自前で作成したのですが、プリントパターンを印刷して確認しなかったこともあり、樹脂部の爪用の穴の位置が若干ずれてしまっていてうまく入りませんでしたorz

樹脂の突起部分用の穴の内側をヤスリで少し削りました。ガラエポといってもヤスリで簡単に削れるので作業は楽です。

少し削った結果、パチッとハマるようになりました。

部品実装後のトップ面が下の写真です。ICの刻印が写るようにライトの位置を調整しましたが少しテカってしまいました^^;

ボトム面が下の写真です。基板設計時にRCAジャックの基板の淵からの出っ張り具合を少し悩みましたが、丁度いい感じですね。

自作CPU関連の作業がこのところ滞ってしまっていますが、今回は部品実装までです^^;

今回設計したSimpl8VDPSG基板はSimple8バスでVDP(TMS9918)とPSG(AY-03-8910)を制御できるので制御用のZ80ボードも欲しくなってしまいますね。

一体化するとこんな感じです。DCジャックの高さもギリギリできわどかったw

★追記 2021/06/20

本来ならCPU基板を上側にした方がアドレスバスのLED等も見易くなりいいのですが、今回プリント基板化したVDPSG基板のディバッグを行うためにはVDPSGが上側の方が信号の確認がやり易いのでこの順番で積み上げています。

将来的には逆順にしたいと思っています。

[TOP] [ 前へ ] 連載記事 [ 次へ ]

今回は5枚発注したのですがなんと11枚届きました(ELECROWさんではいつも1枚くらい余分に届くのですが今回なんと+6枚w)。

5枚手配したのがどこかで10枚手配の扱いになったようです。また、配達が完了してから発送通知(しかも添付の写真無し)が届きました。

コロナ禍の為か受注処理が少々混乱しているようです。

今回は発送方法を佐川さん(以前は選択肢になかった)に指定したことと残っていたポイントを使ったので結構安く上がりました。

| SUBTOTAL | $4.90 |

| REWARDPOINTS(USED 196) | -$1.96 |

| SHIPPING & HANDLING | $7.30 |

| ESTIMATED TOTAL | $10.24 |

|---|

出来上がったプリント基板のトップ面が下の写真です。外観的には特に問題なく綺麗に仕上がっています。

| Simple8VDPSG基板のトップ面 |

|

|

ボトム面も綺麗にできています。

| Simple8VDPSG基板のボトム面 |

|

|

今回使用したRCAジャック(NTSC出力用と音声出力用)は共立エレショップさんから購入したホシデン製のものでフットプリントを自前で作成したのですが、プリントパターンを印刷して確認しなかったこともあり、樹脂部の爪用の穴の位置が若干ずれてしまっていてうまく入りませんでしたorz

| RCAジャック実装部 |

|

|

樹脂の突起部分用の穴の内側をヤスリで少し削りました。ガラエポといってもヤスリで簡単に削れるので作業は楽です。

| RCAジャック実装部の手加工 |

|

|

少し削った結果、パチッとハマるようになりました。

| RCAジャック実装部の加工後の実装確認 |

|

|

部品実装後のトップ面が下の写真です。ICの刻印が写るようにライトの位置を調整しましたが少しテカってしまいました^^;

| Simple8VDPSG基板のトップ面 |

|

|

ボトム面が下の写真です。基板設計時にRCAジャックの基板の淵からの出っ張り具合を少し悩みましたが、丁度いい感じですね。

| Simple8VDPSG基板のボトム面 |

|

|

自作CPU関連の作業がこのところ滞ってしまっていますが、今回は部品実装までです^^;

今回設計したSimpl8VDPSG基板はSimple8バスでVDP(TMS9918)とPSG(AY-03-8910)を制御できるので制御用のZ80ボードも欲しくなってしまいますね。

★追記 2021/06/20

CPU基板と重ねるためのスペーサーを3Dプリンタで作りました。下側の基板の足も兼用するようにしました。

CPU基板と重ねるためのスペーサーを3Dプリンタで作りました。下側の基板の足も兼用するようにしました。

| スペーサー |

|

|

一体化するとこんな感じです。DCジャックの高さもギリギリできわどかったw

| VDPSG on Simple8Z |

|

|

★追記 2021/06/20

本来ならCPU基板を上側にした方がアドレスバスのLED等も見易くなりいいのですが、今回プリント基板化したVDPSG基板のディバッグを行うためにはVDPSGが上側の方が信号の確認がやり易いのでこの順番で積み上げています。

将来的には逆順にしたいと思っています。

[TOP] [ 前へ ] 連載記事 [ 次へ ]

SuperSimpleController(その17)TMS9918Aの接続 その2 [OriginalCPU]

前回の記事でMSXで使われていたVDP(TMS9918A)を使って自作CPU(Simple8Z)でHello表示できたことを書きましたが、ブレッドボードでは動作が不安定なのでプリント基板化してみることにしました。

前回の記事の末尾に追記したようにVRAMに4bitのDRAMを使う場合は後継のTMS9118を使った方が回路が簡略化できますが、TMS9918Aに4bitのDRAMを接続した例がネット上では見つからなかったので今回は敢えてTMS9918Aを使うことにします。また、TMS9118は値段が高いのでTMS9918を使った方がチップ数は増えても費用は安くなります。

MC68B50を使ったシリアルインターフェースを追加しても10cm角の基板では余裕があるので、MSXで使われていたPSG(AY-3-8910)もついでに実装することにしました。

下図がAliExpressで購入した単価¥65のPSGです。見るからに再生品(特に一番上のものは左側の丸い窪みが無くなっている)ですが、果たして動作するのでしょうか?

中華製の廉価なAY-3-8910はYM2149のリマーク品が多いという情報を見つけました(CHEAP “AY-3-8910” ARE ACTUALLY YM2149’S)が互換チップのYM2149には若干機能追加がなされているようです(なのでYM2149だとしても困らないはずです)。

DRAMも追加購入したので写真を貼っておきます。複数種類のマーキングのものが混在していて、一番右のもの以外はピンも広がっていたので再生品ではないようです。

いつもはブレッドボードで確認してからプリント基板化するのですが、今回はPSG部分はブレッドボードでの検証無しにプリント基板化してみます。

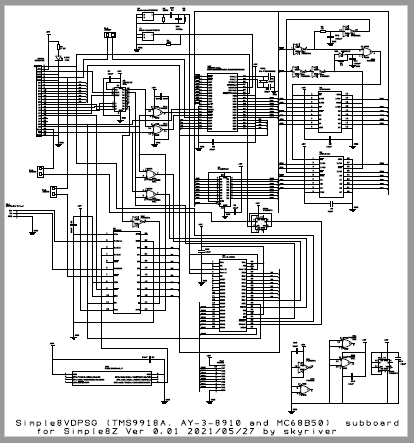

作成した回路図が下記になります。SIMPLE8のインターフェースで制御可能なVDPとPSGを実装しているのでボード名称をSimple8VDPSGとしました(上述のようにシリアルインターフェースも実装しています)。

★追記 2021/08/29 {

「SuperSimpleController(その23)VDPSG基板の改版」の記事に修正した回路図とパターン図を記載しました。

}

今回は12チップ構成ですが小ぶりのチップが多いのでパターン設計は前回のCPU本体よりはかなり楽でした。

グランドベタ化前のパターン図を下図に示します。左上のDRAM部分はパターンが結構込み入っています。

グランドベタ化後のトップ及びボトムのパターンが下図になります。

3D表示したものも貼っておきます。

★追記 2021/05/28

使用しているCADはDesignSparkPCB 8.1.2ですがシルク印刷の位置が拡大率によってズレる現象が発生したのでサンプルを貼っておきます。

フォントは「MS UI Gothic」を使用しています。

[TOP] [ 前へ ] 連載記事 [ 次へ ]

前回の記事の末尾に追記したようにVRAMに4bitのDRAMを使う場合は後継のTMS9118を使った方が回路が簡略化できますが、TMS9918Aに4bitのDRAMを接続した例がネット上では見つからなかったので今回は敢えてTMS9918Aを使うことにします。また、TMS9118は値段が高いのでTMS9918を使った方がチップ数は増えても費用は安くなります。

MC68B50を使ったシリアルインターフェースを追加しても10cm角の基板では余裕があるので、MSXで使われていたPSG(AY-3-8910)もついでに実装することにしました。

下図がAliExpressで購入した単価¥65のPSGです。見るからに再生品(特に一番上のものは左側の丸い窪みが無くなっている)ですが、果たして動作するのでしょうか?

中華製の廉価なAY-3-8910はYM2149のリマーク品が多いという情報を見つけました(CHEAP “AY-3-8910” ARE ACTUALLY YM2149’S)が互換チップのYM2149には若干機能追加がなされているようです(なのでYM2149だとしても困らないはずです)。

| 海外通販で購入した PSG(AY-3-8910) |

|

|

DRAMも追加購入したので写真を貼っておきます。複数種類のマーキングのものが混在していて、一番右のもの以外はピンも広がっていたので再生品ではないようです。

| 海外通販で購入した 64K x 4bitのDRAM(D41464) |

|

|

いつもはブレッドボードで確認してからプリント基板化するのですが、今回はPSG部分はブレッドボードでの検証無しにプリント基板化してみます。

作成した回路図が下記になります。SIMPLE8のインターフェースで制御可能なVDPとPSGを実装しているのでボード名称をSimple8VDPSGとしました(上述のようにシリアルインターフェースも実装しています)。

★追記 2021/08/29 {

「SuperSimpleController(その23)VDPSG基板の改版」の記事に修正した回路図とパターン図を記載しました。

}

| Simple8VDPSGボードの回路図 |

|

今回は12チップ構成ですが小ぶりのチップが多いのでパターン設計は前回のCPU本体よりはかなり楽でした。

グランドベタ化前のパターン図を下図に示します。左上のDRAM部分はパターンが結構込み入っています。

| トップ及びボトム両面のパターン(グランドベタ化前) |

|

|

グランドベタ化後のトップ及びボトムのパターンが下図になります。

| Simple8VDPSGボードのトップ面パターン |

|

|

| Simple8VDPSGボードのボトム面パターン |

|

|

3D表示したものも貼っておきます。

| Simple8VDPSGボードの3D表示 |

|

|

★追記 2021/05/28

使用しているCADはDesignSparkPCB 8.1.2ですがシルク印刷の位置が拡大率によってズレる現象が発生したのでサンプルを貼っておきます。

フォントは「MS UI Gothic」を使用しています。

| 拡大時は'G'が右端のピンの上で問題無し | 縮小表示時にずれた表示例 |

|

|

|

[TOP] [ 前へ ] 連載記事 [ 次へ ]

SuperSimpleController(その16)TMS9918Aの接続 [OriginalCPU]

前回の記事ではオリジナルCPU(Simple8Z)での整数演算処理と逆ポーランド式電卓の作成について書きましたが、TeraTermの画面で処理するだけではあまり面白くないのでグラフィック画面を表示できるようにしたいと思います。

グラフィック表示機能をTTLで作るのも面白そうではありますが、今回はいにしえのMSXで使われていたTMS9918Aという画面表示プロセッサ(VDP)を使うことにします。

当時は16KB x 1bitのDRAM(4116)を8個付けるのが標準的な回路でした(TMS9918のデータシートにも4116の接続例が書いてありますし、Video Display Processorのサイトの「RAM interface」の箇所には具体的な接続が書いてあり参考になります)

また、ネット上ではRASとCAS信号で多重化されたアドレス信号を574等で分離することでSRAMを接続する回路例も見つかります。

★追記 2021/11/10 {

TMS9918Aに接続される8個のDRAMをSRAM化する元情報と思われる資料を見つけたのでリンクを貼っておきます。今回の試みであるTMS9918での4bit DRAM対応は使用チップ数も少なく、自分的にはかなり面白い試みだと思います。

下記のリンク資料で最後の方にTMS91x8について言及されています。興味深いのはTMS9918用のSRAM化回路でDRAMへのライト時のデータバス切替え用のD-FF(74LS574)をソケットから抜けばTMS91x8に差し換えても動作すると書かれていることです。

そうであれば、今回開発している4bit DRAM化回路でも同じことが言えるはずです。}

SRAMを使うためにラッチのICを2つ使うよりも手持ちのuPD41464(64KB x 4bitのDRAM)を使えたら、より簡略な回路にできるのではないかと考えて挑戦してみました。一応ネットでも探してみましたがTMS9918に4BITのDRAMを接続した回路は見つかりませんでした。

今回は自作のオリジナルCPU(Simple8Z)でコントロールするのでVDP周りは既知の実績のある回路を採用した方が断然楽なのですが、敢えて未踏の構成に挑戦するというのは趣味としての醍醐味でもあります。

始めにTMS9918Aのデータシートに記載されているVRAMのリード/ライト時の信号タイミング図を下図に示します。

リード/ライト制御信号が1つの信号なのは6116自体がデータ入力とデータ出力のピンが別々でリード専用の制御信号が無いためです。今回使用する41464のデータピンは一つで双方向になっていてリード(OE/)とライト(WE/)の制御信号が必要です。

41464のデータシートに記載されているリード及びライトのタイミング図を貼っておきます。ライトサイクルにはEarly Write CycleとOE-controlled Write Cycleの二通りありますが、今回採用した後者のみを貼りました。

TMS9918Aと41464のタイミングを見比べてみるとリードサイクルはまぁいいとしてもライト時にはOE/がアクティブにならないようにする必要があります。これはCASを一定時間ディレーした信号を作り、リード信号(ライト信号を反転したもの)とANDをとることでライト時にOE/がアクティブにならないようにしました(その他、NOTゲートを使ったタイミング調整等も行い、DRAMをアクセスできるようになりました)。

また、ライト時にはライトデータがアドレス線と同じバス(ADn)に多重化されて出力されるので3ステートのバッファを介して41464のデータピンに接続しました。下図のMRW/信号はTMS9918Aから出力されるR/W信号です。

具体的な回路図については動作確認後に別途ブログに記載する予定です。

現時点での41464への制御信号の実測例を下図に示します。

1:RAS/、2:CAS/、3:WE/、4:OE/ の信号で、中央部分がライトサイクルでその前後がリードサイクルです。

TMS9918Aのグラフィック1(モード0)を使って動作確認を行っています。VRAMのマッピングはMSXのSCREEN1に合わせました。

色々いじくり回した結果、オリジナルCPU(Simple8Z)を使ってやっとHelloが表示できました^^/

ビデオ出力部はTMS9918Aのデータシートに書いてあるように330Ωでプルダウンしただけですが、トランジスタ回路にするともっと綺麗になるかもしれません。

下図はHello表示した際にNTSC信号をキャプチャしたもので記念に貼っておきます(手持ちの安いLCD式の小型モニタでも表示できました)。

上記の内容はブレッドボードを使って評価中で、オリジナルCPUのI/O拡張用コネクタピンから信号線を取り出し、ブレッドボードに接続しています。ブレッドボード上にはモニタを動かすためにMC68B50を使ったシリアルインターフェースも組み込んでいます。

いつもながらに混沌としていますがブレッドボードと接続した写真も貼っておきます。

今のところ、オリジナルCPU側のマイクロコードの修正等は発生していません。

★追記 2021/05/15

TMS9918のバリエーションとして4BitのDRAMに対応したTMS9118があります。

VRAMのライトサイクルのタイミングが下図のようになっていてW/信号がCAS/より前にアクティブになるので、そのままでDRAMの Early Write Cycle に対応できます。

また、ライトデータがアドレス線に多重化されていないので上記のTMS9918Aのようなバッファリングも不要になります。

[TOP] [ 前へ ] 連載記事 [ 次へ ]

グラフィック表示機能をTTLで作るのも面白そうではありますが、今回はいにしえのMSXで使われていたTMS9918Aという画面表示プロセッサ(VDP)を使うことにします。

当時は16KB x 1bitのDRAM(4116)を8個付けるのが標準的な回路でした(TMS9918のデータシートにも4116の接続例が書いてありますし、Video Display Processorのサイトの「RAM interface」の箇所には具体的な接続が書いてあり参考になります)

また、ネット上ではRASとCAS信号で多重化されたアドレス信号を574等で分離することでSRAMを接続する回路例も見つかります。

★追記 2021/11/10 {

TMS9918Aに接続される8個のDRAMをSRAM化する元情報と思われる資料を見つけたのでリンクを貼っておきます。今回の試みであるTMS9918での4bit DRAM対応は使用チップ数も少なく、自分的にはかなり面白い試みだと思います。

下記のリンク資料で最後の方にTMS91x8について言及されています。興味深いのはTMS9918用のSRAM化回路でDRAMへのライト時のデータバス切替え用のD-FF(74LS574)をソケットから抜けばTMS91x8に差し換えても動作すると書かれていることです。

そうであれば、今回開発している4bit DRAM化回路でも同じことが言えるはずです。}

SRAMを使うためにラッチのICを2つ使うよりも手持ちのuPD41464(64KB x 4bitのDRAM)を使えたら、より簡略な回路にできるのではないかと考えて挑戦してみました。一応ネットでも探してみましたがTMS9918に4BITのDRAMを接続した回路は見つかりませんでした。

今回は自作のオリジナルCPU(Simple8Z)でコントロールするのでVDP周りは既知の実績のある回路を採用した方が断然楽なのですが、敢えて未踏の構成に挑戦するというのは趣味としての醍醐味でもあります。

始めにTMS9918Aのデータシートに記載されているVRAMのリード/ライト時の信号タイミング図を下図に示します。

| TMS9918AのVRAMリードサイクル |

|

|

| TMS9918AのVRAMライトサイクル |

|

|

リード/ライト制御信号が1つの信号なのは6116自体がデータ入力とデータ出力のピンが別々でリード専用の制御信号が無いためです。今回使用する41464のデータピンは一つで双方向になっていてリード(OE/)とライト(WE/)の制御信号が必要です。

41464のデータシートに記載されているリード及びライトのタイミング図を貼っておきます。ライトサイクルにはEarly Write CycleとOE-controlled Write Cycleの二通りありますが、今回採用した後者のみを貼りました。

| 41464のリードサイクル |

|

|

| 41464のライトサイクル(OE-controlled Write Cycle) |

|

|

TMS9918Aと41464のタイミングを見比べてみるとリードサイクルはまぁいいとしてもライト時にはOE/がアクティブにならないようにする必要があります。これはCASを一定時間ディレーした信号を作り、リード信号(ライト信号を反転したもの)とANDをとることでライト時にOE/がアクティブにならないようにしました(その他、NOTゲートを使ったタイミング調整等も行い、DRAMをアクセスできるようになりました)。

また、ライト時にはライトデータがアドレス線と同じバス(ADn)に多重化されて出力されるので3ステートのバッファを介して41464のデータピンに接続しました。下図のMRW/信号はTMS9918Aから出力されるR/W信号です。

| TMS9918Aからのライトデータのバッファリング |

|

|

具体的な回路図については動作確認後に別途ブログに記載する予定です。

現時点での41464への制御信号の実測例を下図に示します。

1:RAS/、2:CAS/、3:WE/、4:OE/ の信号で、中央部分がライトサイクルでその前後がリードサイクルです。

| DRAM(41464)の制御信号波形例 |

|

|

TMS9918Aのグラフィック1(モード0)を使って動作確認を行っています。VRAMのマッピングはMSXのSCREEN1に合わせました。

| VRAMのマッピング |

|---|

PCGAD EQU 0000H ; 0000 - 07FF : pattern generater table VRAMAD EQU 1800H ; 1800 - 1AFF : pattern name table SATRAD EQU 1B00H ; 1B00 - 1B7F : sprite attribute COLTAD EQU 2000H ; 2000 - 201F : color table SPATAD EQU 3800H ; 3800 - 3FFF : sprite pattern |

色々いじくり回した結果、オリジナルCPU(Simple8Z)を使ってやっとHelloが表示できました^^/

ビデオ出力部はTMS9918Aのデータシートに書いてあるように330Ωでプルダウンしただけですが、トランジスタ回路にするともっと綺麗になるかもしれません。

下図はHello表示した際にNTSC信号をキャプチャしたもので記念に貼っておきます(手持ちの安いLCD式の小型モニタでも表示できました)。

| Hello表示画面 |

|

|

上記の内容はブレッドボードを使って評価中で、オリジナルCPUのI/O拡張用コネクタピンから信号線を取り出し、ブレッドボードに接続しています。ブレッドボード上にはモニタを動かすためにMC68B50を使ったシリアルインターフェースも組み込んでいます。

いつもながらに混沌としていますがブレッドボードと接続した写真も貼っておきます。

今のところ、オリジナルCPU側のマイクロコードの修正等は発生していません。

| ブレッドボードでの評価状況 |

|

|

★追記 2021/05/15

TMS9918のバリエーションとして4BitのDRAMに対応したTMS9118があります。

VRAMのライトサイクルのタイミングが下図のようになっていてW/信号がCAS/より前にアクティブになるので、そのままでDRAMの Early Write Cycle に対応できます。

また、ライトデータがアドレス線に多重化されていないので上記のTMS9918Aのようなバッファリングも不要になります。

| TMS9118のVRAMライトサイクル |

|

|

[TOP] [ 前へ ] 連載記事 [ 次へ ]