3チップ構成68Kマイコンの構想(その13)プリント基板完成 [68K]

「3チップ構成68Kマイコンの構想(その11)回路図整理とパターン設計」の記事に書いたように今回は最初からCNCでのプリント基板製造は諦め、プリント基板製造業者に製造を依頼することにしました。

10/8にポチリ、10/24に到着しました。

仕上がり具合は特に問題なく、綺麗に作って貰っています。

今回は青色のソルダレジストにしてみました。トラック幅はCNCで切削し易い設定のままなので太めですw

早々に部品を実装してみましたが、CP/Mが立ち上がりません・・orz

「3チップ構成68Kマイコンの構想」の記事で書いたような簡単なプログラムは動作しましたが、メモリの末尾(0x0007fc00)を使ったPICと68Kとのデータの受け渡しができていないようです・・

簡易的なモニタプログラムを作成して確認してみようかとも思いましたが、PICと68Kとのパラメータ渡しが出来ていない(メモリの先頭ではokのようですが、どの範囲がNGなのか不明)ので68Kからコンソール入出力ができないため、メモリ編集機能を実装することもできません・・・

そこでこんなプログラムを作成してみました。

68K側のプログラムはこんな感じです。EASy68Kを使用しています。

メモリ確認用68Kプログラム

アセンブルしてできたSレコードファイルをバイナリ変換し、picleのステートメントに自動変換後、picleソースに埋め込み、実行した結果は次のとおりでした。

picleソースに埋め込み実行した結果

上の0x0100部のダンプリスト内容から68K側からのメモリアクセスは特に問題無いようです。

0x0400部(実メモリ上のアドレスは0X0007fc00)のダンプ結果からPICからの0X07fc00のアクセスはA18がhighにならずlowの状態(結果0x0003fc00が読める)のようです。

だいぶ状況が判ってきました^^

次にシンクロでA18がhighになった状態の電圧レベルを確認しました(リファレンスとしてA16と比較)

黄色がアドレス信号で紫色はトリガを取るためのBG/信号です。

A16ももう少し高い電圧の方がいいのですが(今回は回路を限界的に簡略化しているのでこれでOKとします・・LEDの数は多めだけどw)、A18は明らかに電圧が低くなっています・・・・

ボードから電源を抜いた状態でA18とGND間の抵抗を計ってみると2.6Kほどでした(他のアドレス線は15K程度)

一応、半田付け状態も確認しましたが、問題なさそうだったのでメモリを抜いてみると抵抗が他のアドレス線と同じ15K程度になりました。

このことからメモリチップが原因である可能性大です。今回使用している512KBのメモリは2個しか持っていないのでブレッドボードで使っているメモリを抜いてPCBに付けてみたところ無事にCP/M-68Kが立ち上がりました(^^)/

消費電流を計ってみたところ、CP/M起動状態での通常時は170mA、SDカードアクセス時に190mA程度でした。

通常時(キー入力待ち状態)は68KはバスをPICに引き渡して何もしていない状態ですが、使用しているMC68008P10はHMOSプロセスで製造されてるので消費電流はスイッチング速度によらず一定です。

最後にCP/M-68Kが動作中のボード写真を貼っておきます^^

メモリはブレッドボードで使用していたものに交換したのでピン番号と信号名の書かれた紙が貼ってありますw

★2018/11/03 追記

「3チップ構成68Kマイコンの構想(その11)回路図整理とパターン設計」の回路図で

にジャンパピンを変え、PICの31ピンから16MHzが出力されるようにconfigを変更、更にバスリクエスト(BR/:low)時にBG/チェックをしなようにPIC側のソフトを変更することで、MC68008P10(10MHz版)への供給クロックを16MHzにしてみました。

この状態でCP/M-68Kを起動したところ、Cold Boot Loaderが出力している「...booting」が表示された後、「ERAC」のLEDが点灯(メモリ実装外のアドレスをアクセス)して反応がなくなりました^^;

(メモリのアクセスタイムは70nsなので大丈夫だと思いますが)やはり68Kの10MHz版では16MHz動作は厳しいようです。

★2018/12/04 追記

ebayで注文していた512KBのSRAMが届いたのでブレッドボード用にラベルの付けたメモリからラベル無しのものに交換しました。

記念として撮った写真を貼っておきます。TOP面のR23がDCジャックと若干干渉気味ですがDCジャック用の丸穴が大きめなので位置調整で何とか入りそう(若干削るといいかも^^;)

初期バージョンとしてはまぁまぁのできではないでしょうか?

[TOP] [ 前へ ] 連載記事 [ 次へ ]

10/8にポチリ、10/24に到着しました。

仕上がり具合は特に問題なく、綺麗に作って貰っています。

今回は青色のソルダレジストにしてみました。トラック幅はCNCで切削し易い設定のままなので太めですw

| PCB Top side |

|

|

| PCB Bottom side |

|

|

早々に部品を実装してみましたが、CP/Mが立ち上がりません・・orz

「3チップ構成68Kマイコンの構想」の記事で書いたような簡単なプログラムは動作しましたが、メモリの末尾(0x0007fc00)を使ったPICと68Kとのデータの受け渡しができていないようです・・

簡易的なモニタプログラムを作成して確認してみようかとも思いましたが、PICと68Kとのパラメータ渡しが出来ていない(メモリの先頭ではokのようですが、どの範囲がNGなのか不明)ので68Kからコンソール入出力ができないため、メモリ編集機能を実装することもできません・・・

そこでこんなプログラムを作成してみました。

- 0x001000~0X07FF00の範囲で0x0100毎にメモリアドレスを書込む。(例 0x001800には0x00001800が書き込まれる)

- 次に0x001000~0X07F000の範囲で0x1000毎にメモリに書き込まれたアドレス値を拾い、0x0100からのメモリ領域に書き込む。

- 0x0100からのメモリ内容を調べることで68Kのメモリアクセス状況を確認する。また、PIC側からメモリダンプを調べることで68Kとのアクセスアドレスが一致しているかを確認する。(※確認は人手で行う)

68K側のプログラムはこんな感じです。EASy68Kを使用しています。

|

アセンブルしてできたSレコードファイルをバイナリ変換し、picleのステートメントに自動変換後、picleソースに埋め込み、実行した結果は次のとおりでした。

|

上の0x0100部のダンプリスト内容から68K側からのメモリアクセスは特に問題無いようです。

0x0400部(実メモリ上のアドレスは0X0007fc00)のダンプ結果からPICからの0X07fc00のアクセスはA18がhighにならずlowの状態(結果0x0003fc00が読める)のようです。

だいぶ状況が判ってきました^^

次にシンクロでA18がhighになった状態の電圧レベルを確認しました(リファレンスとしてA16と比較)

黄色がアドレス信号で紫色はトリガを取るためのBG/信号です。

| A16の信号波形 | A18の信号波形 |

|

|

|

A16ももう少し高い電圧の方がいいのですが(今回は回路を限界的に簡略化しているのでこれでOKとします・・LEDの数は多めだけどw)、A18は明らかに電圧が低くなっています・・・・

ボードから電源を抜いた状態でA18とGND間の抵抗を計ってみると2.6Kほどでした(他のアドレス線は15K程度)

一応、半田付け状態も確認しましたが、問題なさそうだったのでメモリを抜いてみると抵抗が他のアドレス線と同じ15K程度になりました。

このことからメモリチップが原因である可能性大です。今回使用している512KBのメモリは2個しか持っていないのでブレッドボードで使っているメモリを抜いてPCBに付けてみたところ無事にCP/M-68Kが立ち上がりました(^^)/

消費電流を計ってみたところ、CP/M起動状態での通常時は170mA、SDカードアクセス時に190mA程度でした。

通常時(キー入力待ち状態)は68KはバスをPICに引き渡して何もしていない状態ですが、使用しているMC68008P10はHMOSプロセスで製造されてるので消費電流はスイッチング速度によらず一定です。

最後にCP/M-68Kが動作中のボード写真を貼っておきます^^

メモリはブレッドボードで使用していたものに交換したのでピン番号と信号名の書かれた紙が貼ってありますw

| CP/M-68K動作中の写真 |

|

|

★2018/11/03 追記

「3チップ構成68Kマイコンの構想(その11)回路図整理とパターン設計」の回路図で

- PL3

1-2 の接続を解除

- PL4

1-2 -> 2-3 にジャンパピン変更

にジャンパピンを変え、PICの31ピンから16MHzが出力されるようにconfigを変更、更にバスリクエスト(BR/:low)時にBG/チェックをしなようにPIC側のソフトを変更することで、MC68008P10(10MHz版)への供給クロックを16MHzにしてみました。

この状態でCP/M-68Kを起動したところ、Cold Boot Loaderが出力している「...booting」が表示された後、「ERAC」のLEDが点灯(メモリ実装外のアドレスをアクセス)して反応がなくなりました^^;

(メモリのアクセスタイムは70nsなので大丈夫だと思いますが)やはり68Kの10MHz版では16MHz動作は厳しいようです。

★2018/12/04 追記

ebayで注文していた512KBのSRAMが届いたのでブレッドボード用にラベルの付けたメモリからラベル無しのものに交換しました。

記念として撮った写真を貼っておきます。TOP面のR23がDCジャックと若干干渉気味ですがDCジャック用の丸穴が大きめなので位置調整で何とか入りそう(若干削るといいかも^^;)

初期バージョンとしてはまぁまぁのできではないでしょうか?

| Pic24CPM68K部品実装写真(top面) |

|

|

| Pic24CPM68K部品実装写真(bottom面) |

|

|

[TOP] [ 前へ ] 連載記事 [ 次へ ]

3チップ構成68Kマイコンの構想(その12)Blocking/Deblocking [68K]

前回の記事でプリント基板化のためのパターン設計について書きましたが、プリント基板製造をSeeedさんに注文し待ち状態です^^

今回はCP/M-68KのSDカードアクセス時のブロッキング/デブロッキング処理を追加しました。

3チップ構成のCP/M-80の時はCP/Mのメモリサイズを最大の64KBにしたいこともあってSDカードアクセス処理でブロッキング/デブロッキング処理には対応していませんでした。

今回のCP/M-68KではBIOSのメモリサイズをあまり気にしなくてもいいこと、及びコマンドのサイズがCP/M-80と比較して大きめなのでコマンド実行時に少し待ち時間が発生してしまうのでブロッキング/デブロッキング処理に対応しました。

SDカードのブロック長は512バイトなのでCP/Mのセクタ(128バイト)の4つ分に該当します。

今回の対応で変更したワークエリアは

の変更を行いました。

BIOS内のWriteSectorコール時にD1レジスタに下記の情報が渡されます。

WriteSector処理での追加処理としては最初にSDバッファがヒット(今回の書込みセクタが含まれている)場合はSDの先読みは不要で含まれていない場合は変更フラグがオンならSDバッファをSDに書き込み後、先読みが必要か判断します。

3)の場合は先読み不要でそれ以外の場合は先読みが必要になります。

DMAの内容をSDバッファに書き込み、変更フラグをオンにし、2)の場合は即座にSDバッファ内容をSDに書き込みます(変更フラグはオフにする)。

ReadSector処理に関してはSDバッファにヒットしている場合はSDバッファからセクタ内容を読み取り、ヒットしない場合は変更フラグがオンの場合SDバッファを書込んだ後、必要なSDブロックの内容をSDバッファに読込みます。

SDバッファにヒットした場合、変更フラグがオンでもSDへの書込みは不要ですが、今回は長時間変更フラグがオンになる(その間、電源断等が発生すると書込み情報が失われる)のを避けるため、ReadSector処理ではありますがSDへの書込みを行うようにしました。

文章で書くと少しややこしいですが、プログラム的には若干の追加で対応可能です。

(ワークエリアはSDバッファが4倍に増えるけどプログラムコードのサイズはあまり増えない)

参考に今回対応したBIOSのReadSectorとWriteSectorの部分の抜粋を以下に貼っておきます。

BIOS内ブロッキング/デブロッキング処理

ブロッキング/デブロッキング対処後の動作例として「XMODEMアプリの作成」の記事で載せたxmodemでのファイル送信中のロジアナ波形のbefore/Afterを貼っておきます。

対処後は下図の赤丸部分に示すようにSDカードのアクセス回数が減少しています。

★2018/10/17 追記

コメントに書いたようにCP/MからBIOSのWriteSectorには新たに確保したブロックの最初のセクタ書込み(D1レジスタ=2)であるという情報が渡されています。

今回はCP/Mのブロックサイズを2048バイトにしているので、この情報からSDカードの4ブロック分(SDカードのブロックサイズは512バイト)、先読み無しで書込んでも問題ないはずなので改善してみました。

ワークエリアとして新たに先読み不要カウンタと先読み無しで書込んだブロック番号の保存用ワークを追加して、念のためにSDカードのブロック番号が連番であることも確認するようにしています。

また、ワークエリアを絶対アドレス指定でアクセスするとコード効率が悪くなるのでアドレスレジスタとのオフセットでアクセスするように一部変更しました。

CP/Mの2ブロック分をバイナリモードで単純に書き込むテストプログラムを作りSDカードへの書込み動作を確認してみました。新規ファイルへの書込み動作のみを確認するためにファイルオープン後の書込み開始前と書込み終了後のファイルクローズ前にキー入力処理を入れることでファイルへの書込み中の波形をロジアナで確認しました。

下のキャプチャがロジアナ波形のBefore/After比較になります。

対処前はCP/Mブロックの最初の書込みだけ先読みがない状態なのでSDへの書込みの4回に3回は先読みが発生しています。

改善後は新規書込みの場合、常に先読み無しでSDカードへの書込みが行われていて想定通りの動作になっています。

今回、CPM.SYSを何度か変更して評価するにあたり、CP/M-68Kで採用されているCP/Mローダのおかげで、AドライブのCPM.SYSファイルを入れ替えてCP/Mを再立ち上げするだけでいいので効率的に作業が出来ました。

CP/Mのファイルセットに含まれているサイズが大きめのDDT68000.68K(431セクタ、54KB)のファイルをpipコマンドで空ディスクにコピーする時間を計ってみたところ 5.2秒から4.9秒に改善されました(あまり変わらないですねw)

[TOP] [ 前へ ] 連載記事 [ 次へ ]

今回はCP/M-68KのSDカードアクセス時のブロッキング/デブロッキング処理を追加しました。

3チップ構成のCP/M-80の時はCP/Mのメモリサイズを最大の64KBにしたいこともあってSDカードアクセス処理でブロッキング/デブロッキング処理には対応していませんでした。

今回のCP/M-68KではBIOSのメモリサイズをあまり気にしなくてもいいこと、及びコマンドのサイズがCP/M-80と比較して大きめなのでコマンド実行時に少し待ち時間が発生してしまうのでブロッキング/デブロッキング処理に対応しました。

SDカードのブロック長は512バイトなのでCP/Mのセクタ(128バイト)の4つ分に該当します。

今回の対応で変更したワークエリアは

- PICと68K間のSDデータ渡し用の領域(SDバッファ)を128バイトから512バイトに変更

- SDバッファ内のデータがSDに書き込み済みでない場合の変更フラグを追加

- SDバッファの属性としてsector番号での管理をSDのブロック番号の管理に変更

の変更を行いました。

BIOS内のWriteSectorコール時にD1レジスタに下記の情報が渡されます。

- d1.w = 0 : normal write

- d1.w = 1 : write to a directory sector

- d1.w = 2 : write to first sector of new block

WriteSector処理での追加処理としては最初にSDバッファがヒット(今回の書込みセクタが含まれている)場合はSDの先読みは不要で含まれていない場合は変更フラグがオンならSDバッファをSDに書き込み後、先読みが必要か判断します。

3)の場合は先読み不要でそれ以外の場合は先読みが必要になります。

DMAの内容をSDバッファに書き込み、変更フラグをオンにし、2)の場合は即座にSDバッファ内容をSDに書き込みます(変更フラグはオフにする)。

ReadSector処理に関してはSDバッファにヒットしている場合はSDバッファからセクタ内容を読み取り、ヒットしない場合は変更フラグがオンの場合SDバッファを書込んだ後、必要なSDブロックの内容をSDバッファに読込みます。

SDバッファにヒットした場合、変更フラグがオンでもSDへの書込みは不要ですが、今回は長時間変更フラグがオンになる(その間、電源断等が発生すると書込み情報が失われる)のを避けるため、ReadSector処理ではありますがSDへの書込みを行うようにしました。

文章で書くと少しややこしいですが、プログラム的には若干の追加で対応可能です。

(ワークエリアはSDバッファが4倍に増えるけどプログラムコードのサイズはあまり増えない)

参考に今回対応したBIOSのReadSectorとWriteSectorの部分の抜粋を以下に貼っておきます。

|

ブロッキング/デブロッキング対処後の動作例として「XMODEMアプリの作成」の記事で載せたxmodemでのファイル送信中のロジアナ波形のbefore/Afterを貼っておきます。

| Before |

|

|

対処後は下図の赤丸部分に示すようにSDカードのアクセス回数が減少しています。

| After |

|

|

★2018/10/17 追記

コメントに書いたようにCP/MからBIOSのWriteSectorには新たに確保したブロックの最初のセクタ書込み(D1レジスタ=2)であるという情報が渡されています。

今回はCP/Mのブロックサイズを2048バイトにしているので、この情報からSDカードの4ブロック分(SDカードのブロックサイズは512バイト)、先読み無しで書込んでも問題ないはずなので改善してみました。

ワークエリアとして新たに先読み不要カウンタと先読み無しで書込んだブロック番号の保存用ワークを追加して、念のためにSDカードのブロック番号が連番であることも確認するようにしています。

また、ワークエリアを絶対アドレス指定でアクセスするとコード効率が悪くなるのでアドレスレジスタとのオフセットでアクセスするように一部変更しました。

CP/Mの2ブロック分をバイナリモードで単純に書き込むテストプログラムを作りSDカードへの書込み動作を確認してみました。新規ファイルへの書込み動作のみを確認するためにファイルオープン後の書込み開始前と書込み終了後のファイルクローズ前にキー入力処理を入れることでファイルへの書込み中の波形をロジアナで確認しました。

下のキャプチャがロジアナ波形のBefore/After比較になります。

対処前はCP/Mブロックの最初の書込みだけ先読みがない状態なのでSDへの書込みの4回に3回は先読みが発生しています。

| Before |

|

|

改善後は新規書込みの場合、常に先読み無しでSDカードへの書込みが行われていて想定通りの動作になっています。

| After |

|

|

今回、CPM.SYSを何度か変更して評価するにあたり、CP/M-68Kで採用されているCP/Mローダのおかげで、AドライブのCPM.SYSファイルを入れ替えてCP/Mを再立ち上げするだけでいいので効率的に作業が出来ました。

CP/Mのファイルセットに含まれているサイズが大きめのDDT68000.68K(431セクタ、54KB)のファイルをpipコマンドで空ディスクにコピーする時間を計ってみたところ 5.2秒から4.9秒に改善されました(あまり変わらないですねw)

[TOP] [ 前へ ] 連載記事 [ 次へ ]

3チップ構成68Kマイコンの構想(その11)回路図整理とパターン設計 [68K]

前回の記事で書いたようにCP/M-68K用のXMODEMを作り、ネットで公開されているCP/M-68Kのアプリで容易に遊べるようになったので回路図の整理とプリント基板のパターンを設計してみました。

今回の回路はCP/M-80が動く3チップ構成のPic24CPMと回路構成は共通点が多いです。

今回は最初からPCB製造をメーカーに出すことを前提にしたのでCNCでの作成のための条件であった「Via処理後はViaが基板面から出っ張るのでTQFPの半田付け作業の邪魔にならないようにTQFPの直下にはViaを打たない」という縛りを無くしました。

この結果、Pic24CPMの回路と比較し、MC68008(48ピン)はZ80(40ピン)よりピン数が多いですが、CP/M-80の時よりボードサイズを数ミリ小さくできました(基板サイズは96 x 66[mm])。

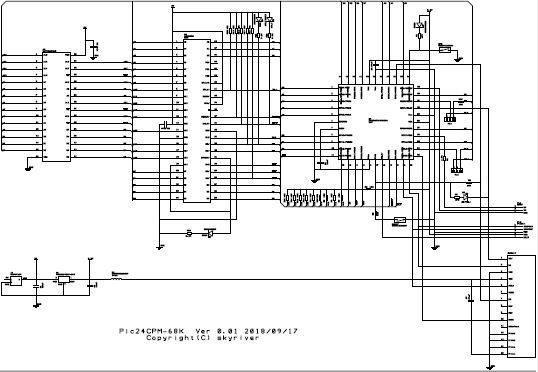

回路図は下図のとおりで使用しているICは

の3チップです。

次にパターン図ですが、上述したように今回はCNCでの基板作成は考慮せず、CNCのための条件もないので自由にパターンを作成しました。

TQFP直下にviaを打ってもいいのでTQFP周辺の反対面(bottom面)のパターンも結構込み入っています。

細い斜めの線はこの時点ではパターン化していないグランドの結線です。グランドをベタパターン化する際に接続される予定です。

下図がグランドベタ化後のトップ面のパターンです。

パターンが込み合っているため、グランドをベタパターンにしても孤立した部分(茶色の部分)が多く発生し、グランドに接続できていなかった端子が何個か生じました。このため数個のviaを追加してトップ面とボトム面を接続することでグランドへのパスが出来るようにしています。

下図はボトム面のパターンです。

おまけでDesignSparkPCBで3D表示した画面を貼っておきます。(上記のトップ面とボトム面接続用のvia追加前のものです)

512KBのSRAM等、3Dデータがないものは直方体になっています。

3チップ構成と言いながら4チップあるように見えますが、右端のICのようなものはSDカードホルダです。w

こんな小さなワンボード基板でCP/M-68Kが動くんですよ^^

★2019/11/25 追記

完成したプリント基板を「3チップ構成68Kマイコンの構想(その13)プリント基板完成」の記事に掲載しました。

[TOP] [ 前へ ] 連載記事 [ 次へ ]

今回の回路はCP/M-80が動く3チップ構成のPic24CPMと回路構成は共通点が多いです。

今回は最初からPCB製造をメーカーに出すことを前提にしたのでCNCでの作成のための条件であった「Via処理後はViaが基板面から出っ張るのでTQFPの半田付け作業の邪魔にならないようにTQFPの直下にはViaを打たない」という縛りを無くしました。

この結果、Pic24CPMの回路と比較し、MC68008(48ピン)はZ80(40ピン)よりピン数が多いですが、CP/M-80の時よりボードサイズを数ミリ小さくできました(基板サイズは96 x 66[mm])。

回路図は下図のとおりで使用しているICは

- MC68008P10

10MHz版のバスが8bit幅の68Kチップ。PICからクロックを供給する関係で8MHzで動作。

- K6T4008C1B-DB70

512KBのSRAM。アクセスタイムは70ns。

- PIC24FJ64GA004

16bitPICマイコン。セルフコンパイラの独自言語picleを使って制御。

の3チップです。

| 3チップ構成の68Kマイコンボードの回路図 |

|

|

★2018/10/31 追記 R3は+5Vにプルアップするつもりでしたが3.3Vへのプルアップでも動作することを確認しました^^; |

次にパターン図ですが、上述したように今回はCNCでの基板作成は考慮せず、CNCのための条件もないので自由にパターンを作成しました。

TQFP直下にviaを打ってもいいのでTQFP周辺の反対面(bottom面)のパターンも結構込み入っています。

細い斜めの線はこの時点ではパターン化していないグランドの結線です。グランドをベタパターン化する際に接続される予定です。

| パターン図(GNDベタ化前) |

|

|

下図がグランドベタ化後のトップ面のパターンです。

パターンが込み合っているため、グランドをベタパターンにしても孤立した部分(茶色の部分)が多く発生し、グランドに接続できていなかった端子が何個か生じました。このため数個のviaを追加してトップ面とボトム面を接続することでグランドへのパスが出来るようにしています。

| トップ面 |

|

|

下図はボトム面のパターンです。

| ボトム面 |

|

|

おまけでDesignSparkPCBで3D表示した画面を貼っておきます。(上記のトップ面とボトム面接続用のvia追加前のものです)

512KBのSRAM等、3Dデータがないものは直方体になっています。

3チップ構成と言いながら4チップあるように見えますが、右端のICのようなものはSDカードホルダです。w

| トップ面 |

|

|

| ボトム面 |

|

|

こんな小さなワンボード基板でCP/M-68Kが動くんですよ^^

★2019/11/25 追記

完成したプリント基板を「3チップ構成68Kマイコンの構想(その13)プリント基板完成」の記事に掲載しました。

[TOP] [ 前へ ] 連載記事 [ 次へ ]